# *High Performance Arithmetic and Logic Unit with Enhanced MTCMOS and Transistor Stacking Techniques*

Esther Rani Thuraka

Department of ECE, CVR College of Engineering Hyderabad, India [estherlawrenc@gmail.com](mailto:estherlawrenc@gmail.com)

Raghava Katreepalli

Department of Electrical Engineering, Navajo Technical University Crownpoint, NM, USA 87313

[rkatreepalli@navajotech.edu](mailto:rkatreepalli@navajotech.edu)

**Abstract**—Short channel devices need lower power supply voltages to reduce power consumption. This forces a reduction in the threshold voltage that causes a substantial increase of weak inversion current. The popular leakage control technique is Multi Threshold Complementary Metal Oxide Semiconductor (MTCMOS) technique. Power gating uses a pMOS transistor and/or an nMOS transistor to disconnect supply voltage from the logic when the logic is inactive by creating virtual  $V_{DD}$  and Ground. This technique can decrease leakage power by more than 50% with negligible delay. For further reduction in the leakage power in deep submicron, a technique known as Enhanced MTCMOS (EMTCMOS) is used which uses a stack of NMOS and PMOS transistors as used in case of MTCMOS technique. EMTCMOS technique condenses leakage further, over the conventional MTCMOS circuits. Transistor stacking is another technique that is verified for leakage power reduction. An Arithmetic and Logic Unit is designed using CMOS, MTCMOS, EMTCMOS and Transistor stacking techniques and compared for the leakage power reduction

**Keywords**—Short Channel; Leakage Power; MTCMOS; EMTCMOS; Transistor Stacking, Arithmetic and Logic Unit;

## I. INTRODUCTION (HEADING I)

In days to come, it is understood that a microprocessor, clocked at 500 MHz with 10cm<sup>2</sup> chip area may consume about 300W. The cost allied with packaging and cooling of such devices is very high. As the essential power consumption must be dissipated through the expensive packaging and also cooling strategies are essential as chip power consumption increases. Peak power known as maximum possible power dissipation is an important design factor because it determines the thermal and electrical limits of designs and further impacts the system size thereby cost, weight based on battery type, system packaging, heat sinks and overstates the resistive and inductive voltage drop problems. It is therefore essential to have the peak power under control.

From the environmental viewpoint, the smaller the power dissipation of electronic systems, the lower the heat pumped into the rooms, the lower the electricity consumed and therefore, the less the impact on global environment. For high performance, in portable computers such as laptops and notebook computers, the goal is to reduce the power dissipation of the electronics portion of the system to a point which is about half of the total power dissipation. Finally, for high performance, the overall goal of power minimization is to reduce system cost and ensure long-term circuit reliability. Low-power design is not only essential for portable applications but also for high-performance systems.

## I. DESIGN OF CMOS OF ARITHMETIC AND LOGIC UNIT

The Arithmetic Logic Unit (ALU) is one of the core components inside a microprocessor and responsible for performing arithmetic and logic operations. The ALU is a vital building block of the Central Processing Unit (CPU) of a computer, and even the simplest microprocessors contain one. The processors found inside modern CPUs and Graphics Processing Units (GPUs) have inside them very powerful ALUs.

Typically, the ALU has direct input and output access to the processor controller, Random Access Memory (RAM) in a personal computer, input/output devices and input and output data in a bus. As per the selection input, the Multiplexer will select corresponding operation and that operation is performed by ALU. ALU has four major components. Arithmetic block performs the core of the arithmetic block is the adder. Logic block performs simple bitwise logic operations. Multiplexers are used to select the appropriate inputs for the arithmetic and logic blocks. Registers can be used to store the data and the results [5]. The ALU designed by using multiplexers and full adder circuit. The multiplexers are designed based on Boolean expression in CMOS design where as full adder circuit is designed with 10-transistors [1,2].

*A. ALU Design and Operation*

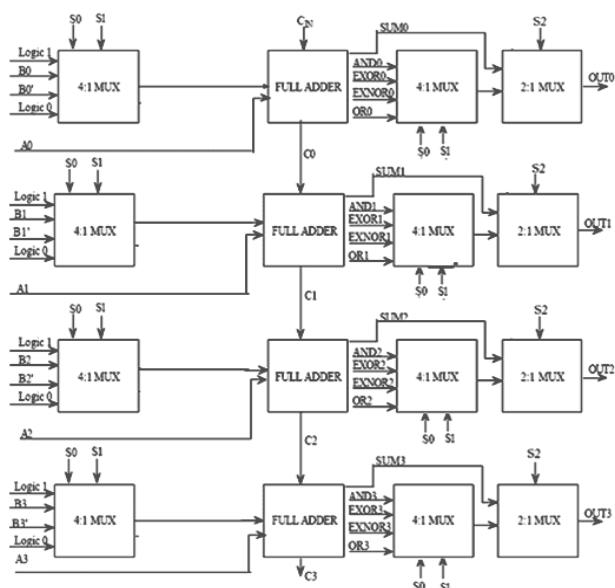

4-bit ALU has been designed with a supply voltage of 1V. The ALU has four stages, each stage consisting of three parts: 1) input multiplexers 2) full adder and 3) output multiplexers as shown in figure 1. The ALU performs four arithmetic and four logical operations. The input and output sections consist of 4x1 and 2x1 multiplexers. The multiplexers are designed using the pass transistor logic. A set of three select signals have been incorporated in the design to determine the operation being performed and the inputs being selected[7,8].

The 4-bit ALU was designed using 90nm, n-well CMOS technology. The INCREMENT and DECREMENT operations logic '1' and logic '0' are applied as inputs respectively. The complement of B input is used for SUBTRACTION. The full adder completes the SUBTRACT operation by two's complement method. An INCREMENT operation is performed by adding '1' to the addend and DECREMENT is the subtraction of 1 from the input and is shown in table 1.

Figure 1: Block diagram of a 4-bit ALU.

Table 1 ALU Operations

| S2 | S1 | S0 | Operation   |

|----|----|----|-------------|

| 0  | 0  | 0  | Addition    |

| 0  | 0  | 1  | Subtraction |

| 0  | 1  | 0  | Increment   |

| 0  | 1  | 1  | Decrement   |

| 1  | 0  | 0  | AND         |

| 1  | 0  | 1  | EXOR        |

|   |   |   |       |

|---|---|---|-------|

| 1 | 1 | 0 | EXNOR |

| 1 | 1 | 1 | OR    |

*B. Full Adder Design*

In ALU, full adder is the essential component of the entire design of ALU especially in this architecture. The full adder performs the arithmetic operations of ALU. One of the outputs of full adder SUM is connected to the input of multiplexer and carry will be sent to the carry bit of the full adder in the next stage. As per selection input signals, the multiplexer stage selects the appropriate inputs and gives it to the full adder. The full adder computes the results. The multiplexer at the output stage selects the appropriate output and sends it out. All the multiplexers have been implemented using pass transistors, but the full adder has been implemented using 10-transistors which include both NMOS and PMOS transistors[4,5].

A full adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of three inputs and two outputs. In this design, the three inputs are A, B and  $C_{in}$ . The input  $C_{in}$  denotes carry input in the first stage. The Boolean expressions for the SUM and CARRY bits are as given below.

$$SUM = AB'C_{in} + A'BC_{in} + A'B'C_{in} + ABC_{in} \quad (1)$$

$$CARRY = AB + AC_{in} + BC_{in} \quad (2)$$

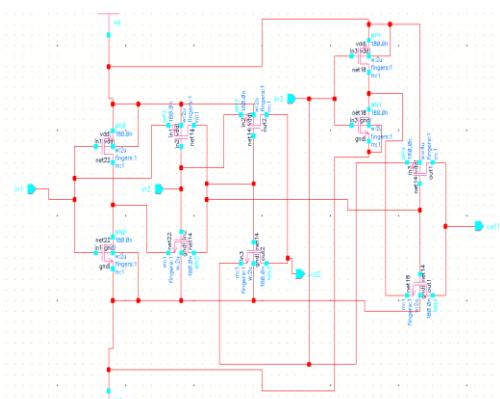

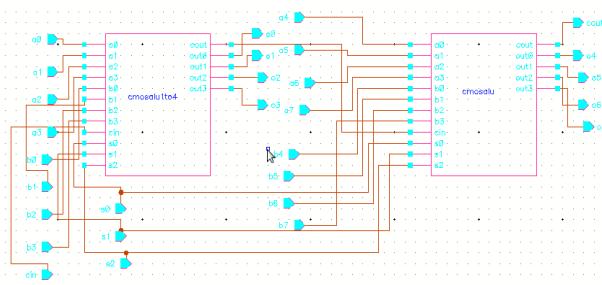

Figure 2 shows the 10 transistor full adder used in the implementation of ALU. This type of circuits have no static and short circuit power dissipation as it does not have complementary pull-up and pull-down circuits [5,6]. Figure 3 shows schematic diagram of CMOS 8-bit ALU, which consists of two 4-bit ALUs.

Figure 2: Schematic of a 10 transistor full adder.

Figure 3. Schematic of CMOS 8-bit ALU

## II. LOW POWER TECHNIQUES

### A. DYNAMIC POWER REDUCTION TECHNIQUES

The quadratic relationship between dynamic power consumption and  $V_{DD}$  conveys that reducing the supply voltage is the most effective way to lower the dynamic power, but gate delay increases. To avoid performance degradation, threshold voltage drop proportional to the supply voltage is necessary so that a sufficient driving current is maintained. The drop in threshold voltage causes an exponential increasing in leakage power, further raises the static power of the device to unacceptable levels. In general, gates of the critical paths operate with higher  $V_{DD}$  or lower  $V_{th}$  and gates on non-critical paths operate at the lower  $V_{DD}$  or higher  $V_{th}$ . Thus total power dissipation is upheld without performance degradation. Power supply scaling also needs support circuitry for low-voltage operation including level-converters and DC/DC converters as well as detailed consideration of issues such as signal-to-noise margins[13].

The power savings that can be achieved by various static and dynamic power management techniques are very application dependent and sometimes substantial. These methods relate with one another in terms of CMOS device scaling or supply voltage scaling. The selection of architecture must be done sensibly and carefully to find an optimum power-area-delay trade-off [3,9].

### B. LEAKAGE OPTIMIZATION TECHNIQUES

Many circuit techniques targeting the reduction of leakage power have appeared in the literature. Most of these techniques target the circuits during the standby operation mode and some target the circuits during the active mode of operation. Few techniques mostly aim to reduce sub-threshold leakage current while others tend to reduce gate leakage current. Transistor stacking, Multi-Vth, Dynamic Vth, Supply Voltage Scaling, Input Vector Control, Body Biasing are the existing techniques for leakage power reduction. A PMOS sleep transistor is used along with body bias and clock gating techniques to reduce the leakage power. A low block reactivation time after exiting the sleep mode is also maintained[11].

#### i. Transistor stacking techniques

All the above-mentioned techniques are applicable when there are two or more stacked transistors which are switched OFF. Sub-threshold leakage current reduces using transistor stacking in two ways. It rises the source bias of upper transistors in the stack and lowers the gate-to-source voltages of these transistors. This results in a lower sub-threshold leakage current. Reduction of leakage using transistor stacks depends on the choice of input pattern during standby periods since it determines the number of OFF transistors in the stack. Leakage current dependencies on circuit state can be exploited and used to determine a low leakage state by using a heuristic search algorithm to find the minimum leakage input vector, which is fed into the circuit during sleep mode.

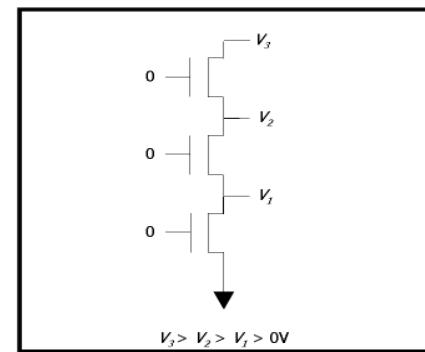

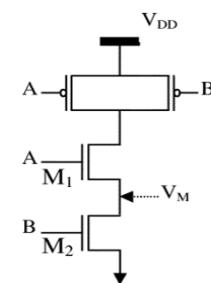

Figure 4: The effect of transistor stacks in reducing  $I_{sub}$

After this input vector is found, the circuit is evaluated and additional leakage control transistors are inserted in the non-critical paths where only one transistor is originally turned OFF. Figure 4 shows the transistors in stack[12].

Sub-threshold leakage current that is flowing through a stack of series-connected transistors decreases when more than one transistor in the stack is turned off. This effect is known as the “stacking effect” or “self reverse bias”. Leakage currents in NMOS or PMOS transistors depend exponentially on the voltage at the four terminals of transistors. When  $V_G$  is ‘0’,  $V_S$  of NMOS transistor increases and reduces sub-threshold leakage current exponentially. A stack of two NMOS transistors as shown in the Figure 5[17,18].

Figure 5: Effect of transistor stacking on source voltage.

#### ii. Multi-Vth techniques

A far more aggressive and effective technique for leakage mitigation is to simply cut the power supply to any inactive transistor. Simply by placing MOS switches in the power network, the ground network or both this is done. The exact sizing and placement of these switches must be done to avoid an adverse impact on performance. This is the most common approach to reduce leakage currents where two different types of transistors are fabricated on the chip. Based on the multi-threshold techniques previously described, several multiple-threshold circuit design techniques have been developed[14-16].

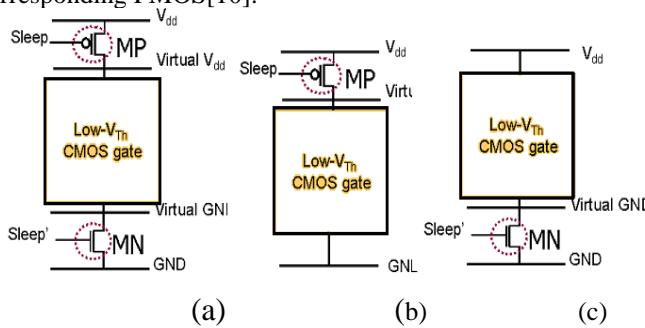

#### iii. Multi-threshold voltage CMOS

Advanced CMOS technology can enable high levels of performance with reduced active power at the expense of increased standby leakage, MTCMOS has previously been described as a method of reducing leakage in standby modes. Reduce the leakage by inserting high-threshold devices in series to low Vth circuitry. Figure 6 (a) shows the schematic of an MTCMOS circuit. In the active mode, Sleep is set to low and sleep control to high Vth transistors (MP and MN) are turned on. As the on-resistance is small, the virtual supply voltages (Virtual Vdd and Virtual GND) almost function as real power lines. In the standby mode, Sleep is set to high, resulting MN and MP to turn off, and the leakage current reduces. Only one type of high Vth transistor is enough for leakage control. Figure 6 (b) and (c) show the PMOS insertion and NMOS insertion schemes, respectively. The NMOS insertion method is preferable, since the NMOS on-resistance is smaller at the same width. NMOS can be sized smaller than corresponding PMOS[10].

Figure 6: MTCMOS Technique (a) pMOS and nMOS sleep devices (b) pMOS Sleep device in the pull-up (c) nMOS sleep device in the pull-down

#### iv. Enhanced MTCMOS

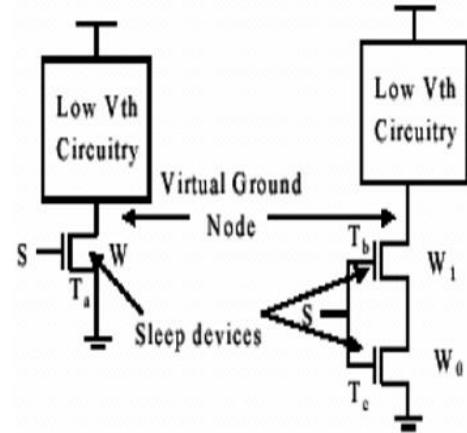

In an enhanced MTCMOS, sub-threshold leakage is reduced in sleep mode due to the added effect of stacking of high threshold voltage transistors. Maximum savings in sub threshold leakage are obtained if the devices in the stack are sized as:

$$W_0 = W/(1-\alpha) \quad (3)$$

$$W_1 = W/\alpha \quad (4)$$

Where  $\alpha = \lambda/(1+2\lambda)$

the lower device in the stack is bigger than the upper device, an increased negative gate-to-source bias and a reduced drain-to-source bias (i.e. reduced DIBL) for the upper device resulting in reduced sub-threshold leakage.

Figure 7: Enhanced MTCMOS technique

Enhanced MTCMOS circuit is shown in figure 7. The average gate leakage is always greater than that for the MTCMOS configuration. The stacked sleep devices can also be sized to maximize the savings in gate leakage factor as

$$W_0 = W(1+\beta) \quad (5)$$

$$W_1 = W[(1+\beta)/\beta] \quad (6)$$

Thus the lower device is required to be bigger than the upper ones a lower gate leakage in the off state optimizing for gate leakage is nearly identical to optimizing for total leakage[19].

### III. ALU USING MTCMOS, ENHANCED MTCMOS AND TRANSISTOR STACKING

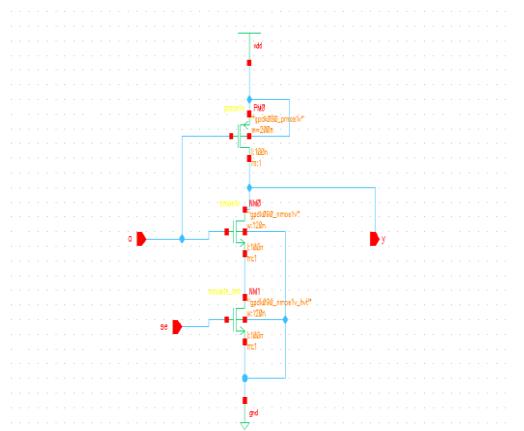

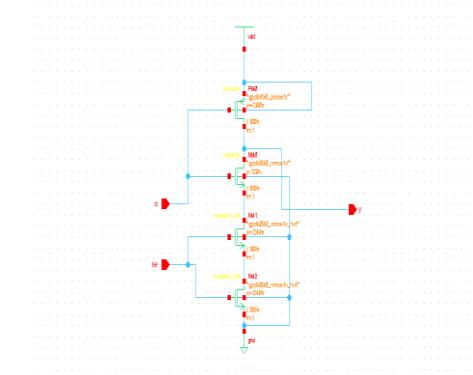

#### A. Implementation of ALU using MTCMOS

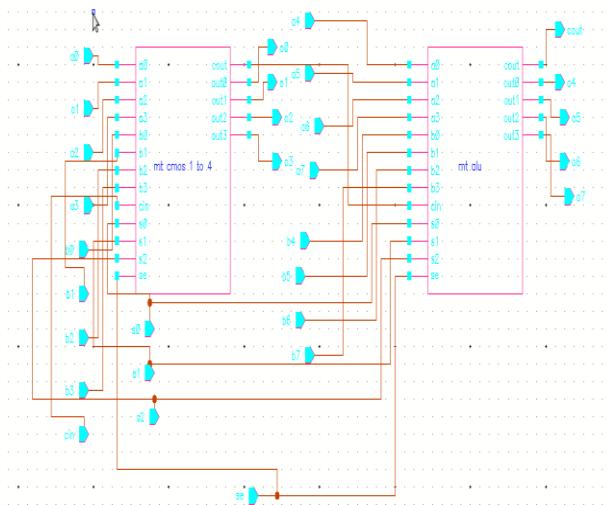

All the blocks of ALU of 2x1 Mux, 4x1 Mux and Full adder are designed using fine grain MTCMOS technique. Figure 8 shows the Inverter using MTCMOS technique. Performance of the ALU can be increased, by reducing the static power dissipation in the circuitry. Figure 9 shows the schematic of 8-bit ALU using MTCMOS. The power dissipation is very less for this ALU when compared to ALU in CMOS implementation.

Figure 8: Inverter using MTCMOS technique

Figure 9: 8-Bit ALU using MTCMOS

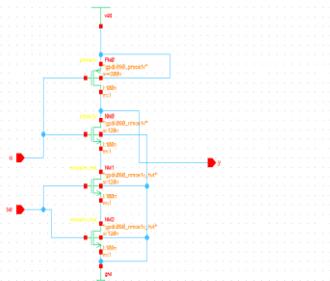

#### B.Implementation of ALU using EMTCMOS

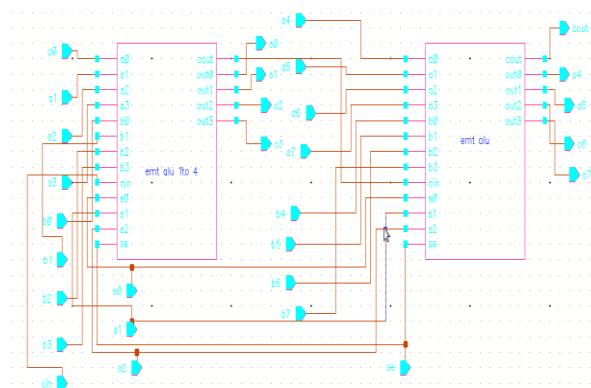

In an enhanced MTCMOS configuration, sub-threshold leakage is reduced in sleep mode due to the added effect of stacking of high threshold voltage transistors. Maximum savings in sub threshold leakage are obtained if the devices in the stack are properly sized. The lower device in the stack is bigger than the upper device. Figure 10 and Figure 11 shows the EMTCMOS Inverter and the 8-bit ALU implemented using EMTCMOS technique respectively.

Figure 10: EMTCMOS Inverter

Figure 11: 8-Bit ALU using EMTCMOS Technique

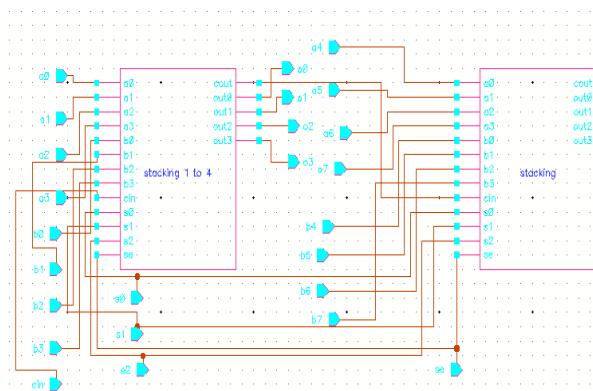

#### C.Implementation Using Transistor Stacking

Sub-threshold leakage current that is flowing through a stack of series-connected transistors decreases when more than one transistor in the stack is turned off. This effect is known as the “stacking effect” or “self reverse bias”. Leakage currents in NMOS or PMOS transistors depend exponentially on the voltage at the four terminals of transistors. Figure 12 and Figure 13 shows the Inverter using transistor stacking and the 8-bit ALU implemented using transistor stacking technique respectively.

Figure 12: Inverter using Transistor stacking

Figure 13: Transistor stacking 8-Bit ALU

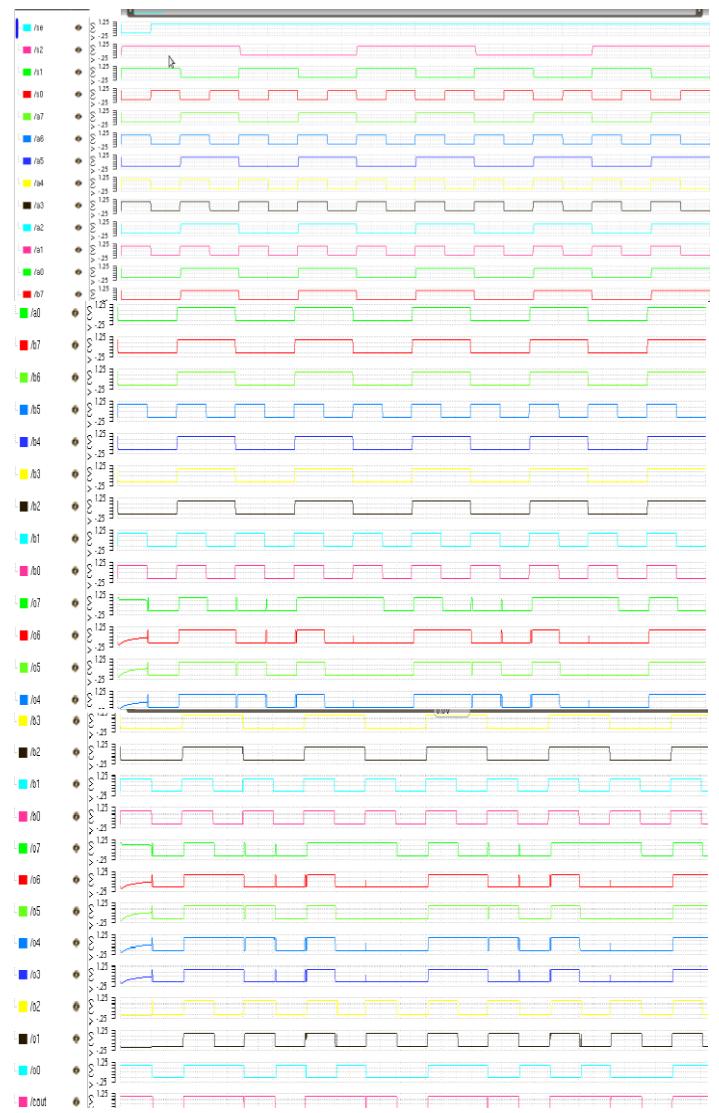

#### IV. RESULTS

Testing environments to check the static and dynamic performance are set up. Though speed is not a major concern in this work, by knowing the conversion time it is convenient to measure the design margin in terms of power and speed. Table 2 and 3 shows the power consumption and the transistor count for an 8-bit ALU. All the eight operations including four arithmetic and four logical operations are verified. ALU implemented using MTCMOS, EMTCMOS and Transistor stacking techniques are also verified and the outputs are observed to be correct. Figure 14 shows the simulation results of 8-bit ALU using three different leakage power reduction techniques.

Table 2 Power consumption of individual cells of ALU

| Module     | CMOS          | MTCMOS        | Transistor Stacking | EMTCMOS        |

|------------|---------------|---------------|---------------------|----------------|

| Inverter   | 58.3 $\eta$ W | 550pW         | 453 pW              | 535 pW         |

| NAND       | 81.6 $\eta$ W | 1.7 $\eta$ W  | 1.6 $\eta$ W        | 1.72 $\eta$ W  |

| NOR        | 80.5 $\eta$ W | 3.77 $\eta$ W | 3.6 $\eta$ W        | 3.74 $\eta$ W  |

| AND        | 256 $\eta$ W  | 1.36 $\eta$ W | 1.3 $\eta$ W        | 1.391 $\eta$ W |

| OR         | 157 $\eta$ W  | 2.67 $\eta$ W | 2.57 $\eta$ W       | 2.5 $\eta$ W   |

| XOR        | 487 $\eta$ W  | 6.6 $\eta$ W  | 5.96 $\eta$ W       | 6.05 $\eta$ W  |

| XNOR       | 575 $\eta$ W  | 4.07 $\eta$ W | 3.75 $\eta$ W       | 3.75 $\eta$ W  |

| 2X1 MUX    | 364 $\eta$ W  | 6.65 $\eta$ W | 3.03 $\eta$ W       | 3.05 $\eta$ W  |

| 4X1 MUX    | 1.67 $\mu$ W  | 16.7 $\eta$ W | 14.66 $\eta$ W      | 15.02 $\eta$ W |

| Full Adder | 3.8 $\mu$ W   | 8.02 $\eta$ W | 7.4 $\eta$ W        | 7.5 $\eta$ W   |

| 8-Bit ALU  | 55.93 $\mu$ W | 26.38 $\mu$ W | 16.85 $\mu$ W       | 16.85 $\eta$ W |

Table 3 Transistor count for the individual cells of ALU

| Module   | CMOS | MTCMOS | Transistor Stacking | EMTCMOS |

|----------|------|--------|---------------------|---------|

| Inverter | 2    | 3      | 4                   | 6       |

| NAND     | 4    | 5      | 6                   | 6       |

| NOR      | 4    | 5      | 6                   | 6       |

| AND      | 6    | 8      | 10                  | 10      |

| OR       | 6    | 8      | 10                  | 10      |

| XOR      | 12   | 15     | 18                  | 18      |

| XNOR     | 14   | 18     | 22                  | 22      |

|            |    |    |    |    |

|------------|----|----|----|----|

| 2X1 MUX    | 12 | 18 | 22 | 22 |

| 4X1 MUX    | 36 | 54 | 66 | 16 |

| Full Adder | 42 | 54 | 66 | 16 |

| 8-Bit ALU  | 42 | 54 | 74 | 74 |

Figure 14: Simulation of 8-Bit ALU

#### CONCLUSION

In this work, an ALU is designed at transistor level using Virtuoso Schematic Editor and simulated using ADEL of Cadence tools. ALU results show that low power and minimum area with good performance is achieved. For large number of computations efficient ALU is to be designed for minimum area and low-power without compromising the high speed. The power consumption of 8-bit ALU is observed to be 26 $\mu$ W for MTCMOS, 16 $\mu$ W for transistor stacking and 16 $\mu$ W

for EMTCMOS. The ALU can be designed for higher bit inputs also. Using this ALU as component, any low power DSP applications can be constructed. Some glitches are observed in the simulation results which consumes extra power. This also can be reduced by considering extra circuitry. Other leakage power reduction techniques can also be compared.

### **Acknowledgment (HEADING 5)**

The authors would like to thank the University Grants Commission, New Delhi, India for sponsoring the research work and CVR College of Engineering for providing infrastructural facilities

### **References**

- [1] R. Shalem, E. John, and L.K.John, "A novel low-power energy recovery full adder cell," in Proc. Great Lakes Symp. VLSI, Feb. 1999, pp.380-383.

- [2] P. Chandrakasan, S.Sheng, and R.W.Broderson, "Low-power CMOS digital design," IEEE J. Solid-State Circuits, vol. 27, pp. 473-483, Apr. 1992.

- [3] R. Pedram and M. Pedram, Low Power Design Methodologies. Norwell, MA: Kluwer, 1996.

- [4] H. T. Bui, A. K. Al-Sheraidah, and Y. Wang, "Design and analysis of 10-transistor full adders using novel XOR-XNOR gates," in Proc. Int.Conf.Signal Processing 2000 (Wold Computer Congress), Beijing, China, Aug. 2000.

- [5] T. Esther Rani, M. Asha Rani and Dr. Rameshwar Rao, "Area Optimized Low Power Arithmetic and Logic Unit," 2011 3rd International Conference on Electronics Computer Technology (ICECT 2011)

- [6] J. Wang, S.Fang, and W.Feng, "New efficient designs for XOR and XNOR functions on the transistor level," IEEE J.Solid-State Circuits, vol.29, pp. 780-786, July 1994

- [7] N.Weste and K.Eshraghian, Principles of CMOS VLSI Design: A System Perspective. Reading, MA: Addison-Wesley, 1993.

- [8] R.Zimmermann and W.Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, pp. 1079-1090, July 1997

- [9] Y.Jiang, Y.Wang, and J.Wu, "Comprehensive Power Evaluation of Full Adders," Florida Atlantic Univ., Boca Raton, Tech. Rep., 2000.

- [10] T.Ester Rani, T. Esther Rani and Dr. Rameshwar Rao, "Area and Power Optimized Multipliers with Minimum Leakage," 2011 3rd International Conference on Electronics Computer Technology (ICECT 2011)

- [11] Meta-Software, HSPICE User's Manual Version H9002, 1992.

- [12] J Chandrakasan, A., and Brodersen, Low Power Digital Design, Kluwer Academic Publishers, R., 1995

- [13] T. Esther Rani and Dr. Rameshwar Rao, "Low Power High Performance Baud Rate Generator using MTMOS Voltage Interface Circuits," International Journal of Engineering Research and Applications (IJERA) Vol. 2, Issue 4, July-August 2012, pp.1621-1626

- [14] Bellaouar, A., and Elmasry, M., Low-Power Digital VLSI Design: circuits and Systems Boston, Massachusetts: Kluwer Academic Publishers, 1995

- [15] Sun,S., and Tsui.P., "Limitation of CMOS supply-voltage scaling by MOSFET threshold voltage" IEEE Journal of Solid-State Circuits, Vol. 30, pp 947-949, 1995

- [16] L.Bisdounis, D.Gouvetas and O.Koufopavou, "A comparative study of CMOS circuit design styles for low power high-speed VLSI circuits" Int. J. of Electronics, Vol.84,No.6, pp599-613,1998.

- [17] Anu Gupta, Design Explorations of VLSI Arithmetic Circuits, Ph.D. Thesis, BITS,Pilani, India, 2003.

- [18] Suzuki, M. et al., "A 1.5-ns 32-b CMOS ALU in double pass-transistor logic" IEEE Journal of Solid-State Circuits, Vol28, pp 1145-1151, 1993

- [19] Y. Yorozu, M. Hirano, K. Oka, and Y. Tagawa, "Electron spectroscopy studies on magneto-optical media and plastic substrate interface," IEEE Transl. J. Magn. Japan, vol. 2, pp. 740-741, August 1987 [Digests 9th Annual Conf. Magnetics Japan, p. 301, 1982].

- [20] M. Young, The Technical Writer's Handbook. Mill Valley, CA: University Science, 1989..