# Grid loss protection in an utility interactive single phase micro string solar inverter

Jeykishan Kumar K<sup>1</sup>

<sup>1</sup>Energy Efficiency and Renewable Energy Division, Central Power Research Institute, Bengaluru, India

[jeykishan@cpri.in](mailto:jeykishan@cpri.in)

**Abstract**— This paper talks about anti-islanding protection function in a 1.5 kVA solar based micro string inverter with considering only the solar input side connected at input and utility connected at output side. As per the Indian standard 16169 which was released in 2014 and equivalent to IEC 62116 standard which was released in the year 2008, any power conditioning unit connected to utility must disconnect from utility within 2s after it goes off-line. The three different voltage levels and total of 47 conditions were tested for various real and reactive power maintaining quality factor 1 at utility side through a 200 kW RLC load and the disconnection time of inverter were obtained through a high definition oscilloscope. For the inverter tested for anti-islanding protection function, it was found that in all scenarios the inverters disconnected well within two seconds as per the limit imposed by IS 16169:2014/IEC 62116:2008.

**Keywords**— inverter, anti-islanding, grid tied, disconnection time, volt-var, volt-watt, IS 16169, IEC 62116

## 1. Introduction

Unintentional islanding of distributed generation may result in power quality issues, interference with grid protection devices, equipment damage, and personnel safety hazards. A comprehensive survey of anti-islanding schemes indicated that existing solutions are too expensive (e.g., transfer trip), not secure (e.g., non-detection zone), or cause power quality degradation (waveform distortion). In an effort to positively enhance the impact of increasing amounts of distributed energy resources, grid-tied photovoltaic (PV) inverters are increasingly being designed to provide advanced Grid Support Functions (GSF) that can provide volt-var and frequency support at their local point of interconnection. Among others, these GSFs include voltage ride-through (VRT), frequency ride-through (FRT), fixed power factor (FPF), volt-var control (VVC), and frequency-watt control (FWC) [1]. Nowadays, almost all photovoltaic and grid-connected inverters have internal protections against islanding. Usually, these protections perform a disconnection from the grid when process variables go beyond over-voltage or under-voltage thresholds, as well as over-frequency or under-frequency thresholds. Furthermore, other schemes like power line communication carrier scheme, slip mode frequency scheme, etc. are often added in commercial equipment. In spite of the importance of anti-islanding protections, it is not easy to test on field thresholds,

reliability and performances of these devices [2]. Islanding occurs when a distributed generation source continues to provide electricity to a portion of the utility grid after the utility experiences a disruption in service. Since the utility no longer controls this part of the distribution system, islanding can pose problems for utility personnel safety, power quality, equipment damage, and restoration of service [3].

## 2. Objective

### 2A. Objective

The primary objective is to validate the effectiveness of anti-islanding protection function in a grid connected or utility interactive type micro string solar inverter. Effectiveness was determined by the speed with which the inverter detected and ceased to energize the utility.

### 2B. Inverter description

The grid tied hybrid inverter is of 1.5 kVA with unity power factor (i.e. 1.5 kW) with a DC voltage range of 22 V to 60 V and 40 A current ranges at DC side. This inverter has 4 input DC slots for solar PV module input with separate MPPT controller and one input each for AC input and AC output for connecting all micro string inverters in series. MPPT voltage was considered from 32 V to 45 V as per manufacturer instruction manual which was further verified through testing.

Fig. 1: Top and side view of the 1.5 kVA micro string inverter

The inverter output AC side is having a voltage range of 202 V to 268 V each phase and 6.09A current range with

frequency range of 48 to 52 Hz. The top and side view of the inverter is shown in Figure 1. Efficiency test was performed as per latest edition of IS/IEC 61683:1999 (Reaffirmed 2015) standard on this 1.5 kVA micro string inverter when connected to the utility, the efficiency was found to be 94.24 % at rated voltage, rated output and rated frequency conditions.

### 3. Islanding Detection

#### 3A. Experimental Setup

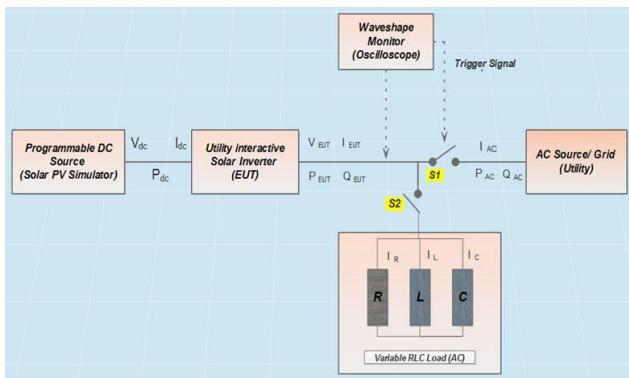

Solar DC input was provided through a solar PV array simulator for feeding DC voltage and current considering the solar PV module parameters. Inverter output is connected to 90 kVA utility system through S1 circuit breaker paralleled with 200 kW (Resistive-inductive-capacitive) RLC load system through S2 circuit breaker. An oscilloscope is connected in parallel with S1 circuit breaker and a small DC source enough to capture a trigger signal when utility disconnects (S1 opened).

Fig 2: Test circuit diagram for grid loss protection test on micro string inverter.

A power analyzer of 4 channels capable to measures both 1 phase AC measurements and DC measurement simultaneously was used to identify the electrical parameters like voltage, current, power factor, harmonics, loss and efficiency of the inverter.  $P_{EUT}$ ,  $P_{AC}$ , and  $Q_{AC}$  indicated in the Figure 2 are inverter output power, real power flow at S1 and reactive power flow at S1 respectively. Positive sign was considered as power flow from inverter to utility. Nominal value is considered as the 0% test condition value.

#### 3B. Anti-islanding detection method

The micro inverter have an over/under frequency protection methods (OFP/UFP) and over/under voltage protection methods (OVP/UVP) that cause the inverter to stop delivering power to the grid if the frequency or amplitude of the voltage at the point of output of inverter and grid lies outside of prescribed limits. This is one of the passive detection methods and will serve as an anti-islanding detection method for this inverter. This method is implemented in software (digital) and the algorithm is based

on the grid voltage detection and it is controlled digitally. The performance of the method at the time of utility disconnection is depended on  $\Delta P$  and  $\Delta Q$  at the instant before the switch opens to form the island. If  $\Delta P \neq 0$ , the amplitude of voltage will change and the OVP/UVP will detect the change and prevent islanding. If  $\Delta Q \neq 0$ , the load voltage will cause a change in phase, and then the inverter's controller system will cause the frequency of the inverter output current, and thus the frequency of voltage (rms), to change until  $\Delta Q=0$ . This change in frequency can be detected by the OFP/UFP. The digital controller senses the grid voltage and frequency through analog to digital converter (ADC) peripheral. A phase locked loop (PLL) algorithm is used to find the change in the frequency and voltage (rms) value. However, when the grid is lost, the algorithm checks the gird frequency shift at the output of inverter with the normal frequency range which is factory set. Then OFP/UFP will stop the power generation if the limits are deviated. This method is implemented in many of Indian micro-inverters because of the low-cost nature of this method.

#### 4. Test Condition

Maximum inverter output power condition is achieved using the maximum allowable input power and the actual output power has exceeded nominal rated output power which is well within the standard scope. Based on inverter's rated input DC operating range which is 22 V to 60 V. But for test condition A as per Table 1 provided, the MPPT voltage range is between 32 volts and 42 volts, inverter has to be supplied with greater than 75% of range which is  $\geq 32 + 0.75 * (45-32)$  V [4]. Y must not exceed 0.8 \* inverter Maximum system voltage (i.e., 60) which is less than 45 V. For test condition B as per Table 1 provided, the voltage level chosen was 50% of voltage range which is obtained by  $32 + 0.5 * (45 - 32)$  V and similarly for the test condition C as per Table 1 provided, the voltage level has to be lesser than 10% of the input voltage range which is  $\leq 32 + 0.1 (45 - 32)$  V.

Table 1: Test conditions

| Test Condition | EUT output power ( $P_{EUT}$ )    | EUT input voltage                            |

|----------------|-----------------------------------|----------------------------------------------|

| A              | Maximum EUT output power          | >90% of rated input voltage range            |

| B              | 50% - 66% of Maximum              | 50% of rated input voltage range, $\pm 10\%$ |

| C              | 25% - 33% of Maximum output power | <10% of rated input voltage range            |

The voltage inputs chosen for this inverter are 44 V, 38.5 V and 33 V for test conditions A, B and C respectively. For test condition A, the voltage level should be maximum and the output power is also 100% and we have considered

44 V as the input DC operating MPPT voltage. This condition has 1 balanced condition and 24 imbalanced conditions. In balanced condition, the total power delivered by the inverter is completely consumed by the RLC load by loading 1.5 kW on resistive load and remaining inductive and capacitive load being equal to 1.5 kVar thereby leading to zero current passing through grid.

Table 2: Load imbalance (real, reactive load) for test condition A with inverter output = 100 %)

| % change in real load, reactive load from nominal |         |        |         |          |

|---------------------------------------------------|---------|--------|---------|----------|

| -10, +10                                          | -5, +10 | 0, +10 | +5, +10 | +10, +10 |

| -10, +5                                           | -5, +5  | 0, +5  | +5, +5  | +10, +5  |

| -10, 0                                            | -5, 0   |        | +5, 0   | +10, 0   |

| -10, -5                                           | -5, -5  | 0, -5  | +5, -5  | +10, -5  |

| -10, -10                                          | -5, -10 | 0, -10 | +5, -10 | +10, -10 |

Table 3: Load imbalance (reactive load) for test condition B & C with Inverter output of 50 % & 33% respectively

| % change in real load, reactive load from nominal |            |

|---------------------------------------------------|------------|

| Inductive                                         | Capacitive |

| 0, -5                                             | 0, 1       |

| 0, -4                                             | 0, 2       |

| 0, -3                                             | 0, 3       |

| 0, -2                                             | 0, 4       |

| 0, -1                                             | 0, 5       |

Table 2 provides the test conditions for A which contains 24 test conditions with various real and reactive power combinations for loading the RLC component with utility. Table 3 shows the real and reactive combinations for test conditions B and C with power out levels at 50% and 33% respectively. Test B and C both contain only 10 conditions each with 5 conditions in inductive load and 5 with capacitive load.

### 5. Test Procedure

This test procedure was incorporated from IS 16169: 2014 standard/ IEC 62116: 2008 [4].

1. Determination of inverter Output Power

2. Adjusting DC input source

- a. S1 closed, S2 opened

- b. Turn inverter ON, Measure inverter power output

- c. Measure real , reactive power, frequency, utility power(real and reactive)

- d. Real power = reactive power for utility

3. Turning OFF inverter and Opening S1

4. Adjusting RLC load to have  $Q_f = 1 \pm 0.05$

- a. Inductive reactance = EUT real power

- b. Inductor as first element

- c. Adjust capacitor to have :  $Q_C + Q_L = - Q$  inverter

- d. Connect resistor to have power consumed by RLC circuit =  $P$  inverter

5. Connecting RLC load as per item 4 and Closing S2.

6. Closing S1 and turning the inverter ON

7. Adjusting RLC to have AC current to be 0 A through S1 with 1 % tolerance

8. Disconnecting S1 to initiate the test.

9. Disconnection time ,  $t_R$  to be recorded

10. For test condition A, adjust real load and only one reactive component by approximately 1 % per test within a total range of 95% to 105%.

11. If run on times are increasing, and then increase 1% increments until run on time decreases.

12. Test C load conditions may be achieved using inverter control to limit output power rather than power supply limit.

The point at which the current ceases to zero is taken into consideration of disconnection time. Some test conditions exhibited voltage not going to zero when current is zero due to design differences, but voltage levels along with current levels were monitored.

### 6. Results

#### 6A. Anti-islanding analysis

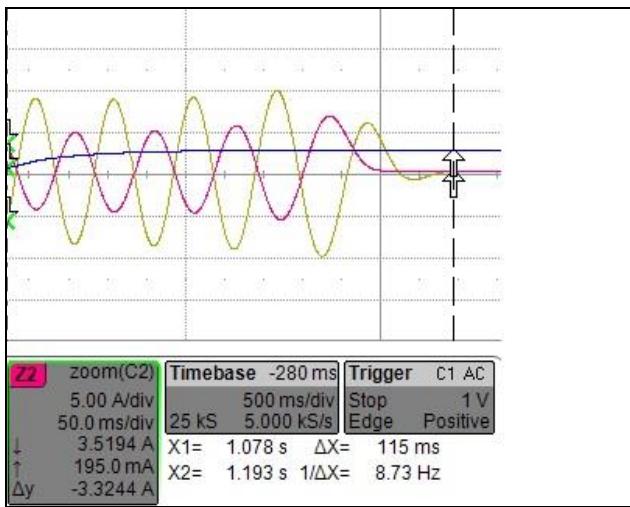

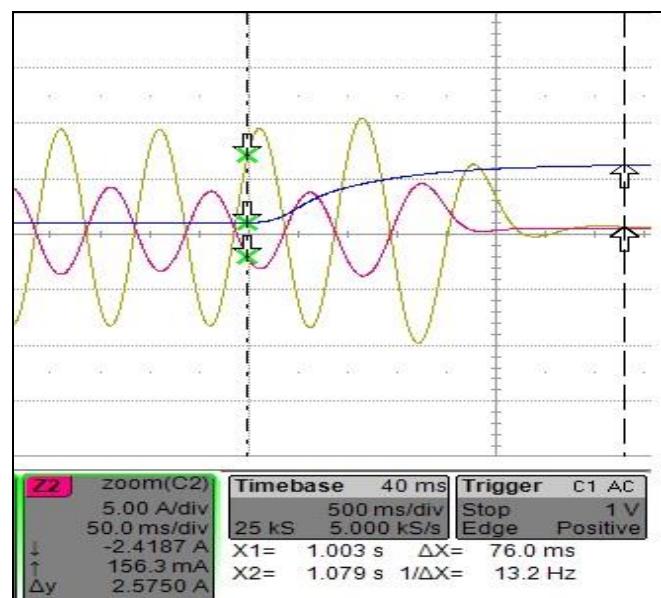

The sample tested is a 1.5 kW grid tied micro string solar inverter having 1 phase 3 wire system. Figure 3 shows the disconnection time of a condition in which the inverter was supplying 100% rated power i.e. 1.5 kW to the load and zero power to grid (balanced condition) with maintaining quality factor of 1. The disconnection time is the time from which the grid goes offline to the current zero point of inverter output. This was measured through an oscilloscope where a trigger signal is generated when the grid goes offline (indicated in blue), voltage of the inverter indication is pale yellow and current from the inverter to the grid is indicated in pink.

The voltage measurement from the individual phase is obtained through a high voltage differential probe of 1000V and the current measurement from individual phase was captured through a current sensor of 20/200 A rating. The trigger signal is obtained from the circuit breaker linked with the utility (S1 of Figure 1) and a DC source of 5V/1A connected in parallel with both circuit breaker and oscilloscope.

Fig. 3: Test result for 100% EUT load under balance condition measured for 1-phase grid tied micro string solar inverter.

Table 4: Average disconnection times under load balanced and load imbalance conditions

| P(EUT), % | Disconnection time (in seconds) |                      |

|-----------|---------------------------------|----------------------|

|           | Balanced Condition              | Imbalanced Condition |

| 100       | 115                             | 122.3                |

| 66        | 107                             | 139.7                |

| 33        | 97                              | 133.9                |

As per the testing standard, the number of test conditions for balanced condition is only 3 with different voltage and power levels. For rated power output condition with imbalanced loading to grid, there are 24 conditions. For 66% and 33% rated output power with voltage level reduced to half and less than 25% of input voltage range, the load imbalance conditions are 10 for each voltage levels.

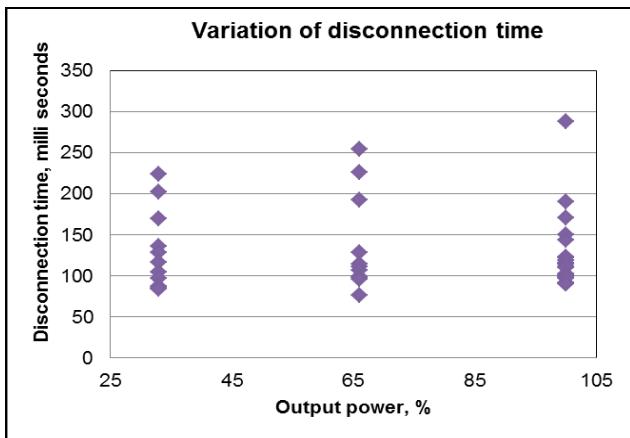

Fig. 4: Variation of disconnection times during anti-islanding condition (47 Nos.) by the 1.5 kW micro string inverter

From Table 4, we can interpret that the disconnection time in balanced condition is higher than imbalance condition for 100% of rated output power of the inverter and similarly the disconnection times at 66% of rated output and at 33% of rated output is higher for imbalance condition than the

balanced condition. It may vary for different types of inverter and may not be applicable to all inverter categories. This disconnection time depends on the circuit design and the topology used for synchronization with utility. Figure 4 provide the disconnection times of the inverter for the various real and reactive power conditions (47 Nos.) at different voltage levels 33%, 66% and 100% power output levels.

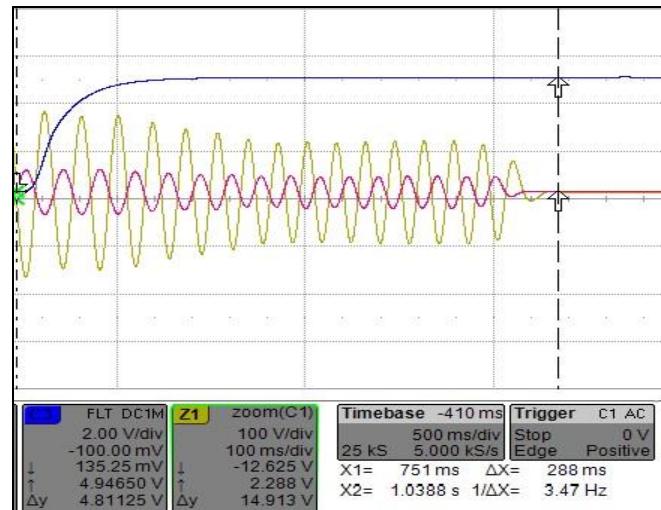

Figure 5: Inverter Voltage and current waveforms recorded from the maximum disconnection time

The disconnection times provided in the Table 4 is disconnection time with real and reactive power variation conditions which were averaged for respective power output requirements totaling to 47 test conditions which were performed on the inverter.

Figure 6: Inverter Voltage and current waveforms recorded from the minimum disconnection time

The maximum disconnection of 288 milli-seconds (ms) is observed and the minimum disconnection time observed is 76 milli seconds. Maximum disconnection time occurred when EUT power output was at 100% and the real power & reactive power drawn by the RLC load (resistive and reactive load) from the grid are both -10% of nominal power i.e. 0.15 kW & 0.15 kVar in which the combined reactive load was inductive in nature. Figure 5 shows the test condition where the maximum disconnection time occurs. Minimum disconnection time occurred when EUT power output was at 66% and the real power & reactive power delivered by the RLC load (resistive and reactive load) to the grid are 0% and +4% (i.e. +60 Var) of nominal power in which the combined reactive load was capacitive in nature. Figure 6 shows the test condition at which the minimum disconnection time occurred.

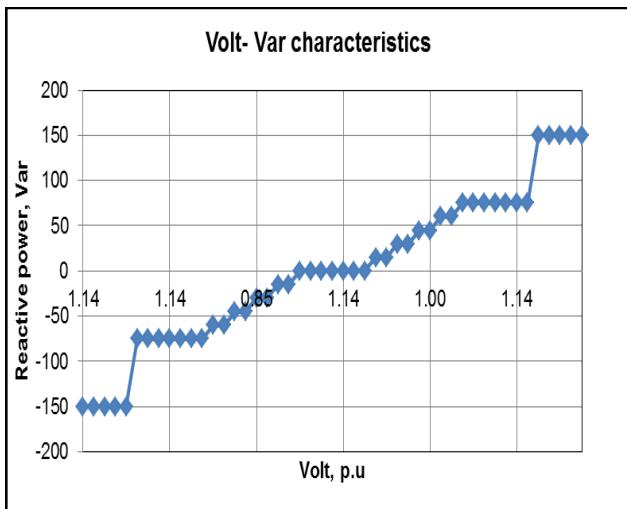

Three different test voltage conditions were used as per the standard with respect to different power output levels. The voltage levels obtained were 220V, 222 V and 224 V for 100%, 66% and 33% output power levels respectively. A 200 kW RLC load was used for varying the real and reactive power conditions as required by the standard for testing the grid functionality of this inverter. The volt-var characteristic shown in Figure 7 indicates that the reactive power changes with change in voltage levels. Ideally the reactive power should be constant with same voltage (red colour), but from the Figure 2, the reactive power is reducing even as the voltage level remained same (green colour).

Figure 7: Volt- var characteristics of 1.5 kW micro string inverter

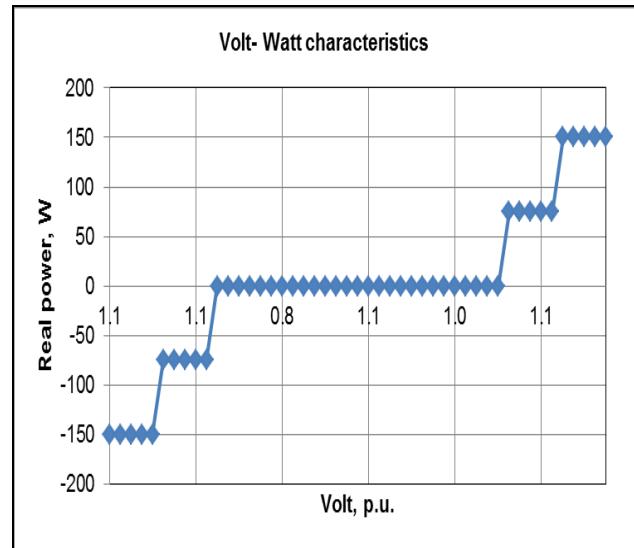

The volt –watt characteristics as shown in the Figure 8 are easily obtained for all inverters as the resistance does not vary much with reactive power variations, but varies a little (negligible) because of the practical inductance( inductance and coil resistance) and the practical capacitance (capacitance and resistance component) being used in this testing. The EUT is considered to comply with the

requirements for islanding protection as per IS 16169:2014/ IEC 62116:2008 and the recorded disconnection times for each condition (as indicated in Figure 4 of this paper) is less than 2 seconds

Figure 8: Volt- watt characteristics of 1.5 kW micro string inverter

#### 6B. Transient Analysis

The transient current in the output of the photovoltaic grid-connected inverters is usually generated when grid voltage sag occurs, which can trigger the protection of the grid-connected inverters, and even destroy the semiconductor switches. Then, the grid-connected inverters will thus fail to ride through the voltage sag and even further cause more serious grid faults [10].

The scope of this paper in regard to the analysis of transients is within the anti-islanding test cases conducted for the inverter under consideration. For all the 47 islanding test cases conducted as per the standard IS 16169 for 1.5 kW solar PV based grid connected single phase micro string inverter, it is observed that the voltage transients are the first to occur immediately after the grid disconnection by increasing to a value of 5% to 40% above the nominal rated output voltage. This change in voltage causes a subsequent change in the rise in current leading to current transients. These current transients were varying between 5% to 40% above nominal output current during the islanding condition for 47 test cases. From the tested cases, the classification of transient study shall be divided to two main conditions. One condition is of balanced case and other is of imbalanced case. Table 5 shows the average current transient duration under balanced and imbalanced conditions. The time of current transients in case of 100%, 66% and 33% output power level of inverter are 4 ms, 10 ms and 21 ms respectively. During inductive loading in case of unbalanced condition, the current transients were present for a duration

of 16 ms, 11 ms and 22 ms for output power levels at 100%, 66% and 33% respectively.

Table 5: Average current transients' duration in milli-seconds under load balanced and load imbalance conditions

| Output Power level, % | Balanced condition | Unbalanced condition |            |

|-----------------------|--------------------|----------------------|------------|

|                       |                    | Inductive            | Capacitive |

| 100                   | 4 ms               | 16 ms                | 20 ms      |

| 66                    | 10 ms              | 11 ms                | 22 ms      |

| 33                    | 22 ms              | 22 ms                | 22 ms      |

During capacitive loading in case of unbalanced condition, the current transients were present for a duration of 20 ms, 22 ms and 22 ms for output power levels at 100%, 66% and 33% respectively. It is observed that in the balanced conditions of different output power levels of inverter i.e. 100%, 66% and 33%, the time of current transients to die out after the overvoltage/ undervoltage is detected is increasing with operating power level of the inverter which could be in capacitive and inductive loading. It is also observed that the voltage transients persist even after current transients die out. This duration of presence of voltage transients are varying from minimum of 5ms to maximum of 50 ms.

During inductive loading, the inverter sees high frequency transients in comparison to capacitive loading wherein low frequency transients were observed. The frequency of current transients during balanced condition is high and has a variation between 45 Hz to 250 Hz in comparison to imbalanced condition which are having variation between 45 Hz to 90 Hz. Further to this, it can also be observed that the transients occurring during inductive loading are higher in comparison to the transients occurring during the capacitive loading. The low value of the observed current transients in regard to the duration or the frequency is because of the inverters low operating output current and power. For voltage transients to die out in small time, then transient voltage suppression diodes could be implemented as they can withstand quick voltage and current spikes [10].

### **Conclusion**

The anti-islanding tests at the laboratory were carried out to evaluate the effectiveness of an interconnection system and anti-islanding protection function based on IS 16169 requirements. Tripping time was used to determine the effectiveness of the protection function. Although testing could show whether protection function was effective, more fine-tuned tests are necessary to find the maximum tripping time under each condition and the correlation between

parameters and tripping time. Analysis were performed on the 1.5 kVA grid tied micro string solar inverter for balanced and un-balanced load condition and identified the maximum and minimum disconnection times when connected to utility for various voltage levels. Solar DC input was provided through a solar PV array simulator for feeding DC voltage and current considering the solar PV module parameters.

For the inverter tested for anti-islanding protection function, it was found that in all scenarios obtained by using a 200 kW RLC load system for different real and reactive power flow conditions the inverter disconnected well within 2 seconds as per the limit imposed by IS 16169:2014/ IEC 62116:2008. Maximum and minimum disconnection times are 288 and 76 milli-seconds. It was also observed that the voltage is not going to zero in certain test cases even after the current settled at zero, this condition is not included in the standard but it could be included in the future amendments. This abnormality of voltage not tending to zero after the disconnection of utility has to be designed inbuilt within the inverter to safeguard the utility and the equipment which are connected to the utility. After each disconnection test case, the voltage transients persist longer than current transients even though the transient levels are low. Low level of current transients is observed and it is because of its low operating current and power of the inverter. The transients observed are all of low frequency transients less than 250 Hz. The frequency of the transients measured during inductive loading are little higher than in the capacitive loading.

In spite of the objective, the inverter here presented was used in the grid tied inverter test laboratory in order to perform tests under real-time simulated conditions. First results are encouraging and they indicate the importance of further improvement. Unquestionably, the increasing photovoltaic market in India increases the importance of this test. Although IS 16169/ IEC 62116 allows for alternative testing procedures, the procedures used for this study should be further used for parallel connection of various DER's or multi inverter scenarios which are the actual and practical implications close to field operation of grid connected solar photovoltaic equipment.

### **Acknowledgements**

This research was supported by Energy Efficiency and Renewable Energy Division of Central Power Research Institute, Bengaluru, Ministry of Power, Govt. of India.

### **References**

[1] A. Nelson, G. Martin, J. Hurt, "Experimental evaluation of grid support enabled PV inverter response to abnormal grid conditions", 2017 IEEE Power & Energy Society Innovative Smart Grid Technologies Conference (ISGT), pp. 1-5, 2017.

[2] Groppi F. "Testing of anti-islanding protections for grid-connected inverters", International Conference on Clean Electrical Power. Piacenza, Italy: IEEE Industrial Electronics Society (IES), 2007 : 183-187.

[3] Ye, Z., Walling, R., Garces, L., Zhou, R., Li, L., and Wang, T.. Study and Development of Anti-Islanding Control for Grid-Connected Inverters. United States: N. p., 2004. Web. doi:10.2172/15007704.

[4] Test Procedure of Islanding Prevention Measures for Utility-Interconnected Photovoltaic Inverters, IS 16169:2014, 2014

[5] R. A. Walling and N. W. Miller, "Distributed generation islanding implications on power system dynamic performance," in *IEEE Power Engineering Society Summer Meeting*, vol. 1, pp. 92–96 vol.1, Jul. 2002.

[6] IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems, Std. IEEE 1547.1, Jul. 2005.

[7] Inverters, Converters, Controllers and Interconnection System Equipment for Use With Distributed Energy Resources, Std. UL1741, 2010.

[8] M. E. AlSharidah, W. G. Dunford, and W. Feng, "A new representation of the unintentional islanding test resonant function," in *INTELEC 2009 - 31st International Telecommunications Energy Conference*, <http://dx.doi.org/10.1109/INTLEC.2009.5351782DOI> 10.1109/INTLEC.2009.5351782, pp. 1–6, Oct. 2009.

[9] T. Caldognetto, L. D. Santa, P. Magnone, and P. Mattavelli, "Power electronics based active load for unintentional islanding testbenches," *IEEE Transactions on Industry Applications*, vol. 53, no. 4, pp. 3831–3839, Jul. 2017.

[10] Li, Z., Zhao, R., Xin, Z., Guerrero, J. M., Savaghebi, M., & Li, P. (2016). Inrush Transient Current analysis and suppression of photovoltaic grid-connected inverters during voltage sag. 2016 IEEE Applied Power Electronics Conference and Exposition (APEC).